Imec and ASML introduced on Wednesday that that they had made the business’s logic and DRAM constructions utilizing ASML’sASML’sroduction Twinscan EXE:5000 EUV lithography device with a 0.55 numerical aperture, often known as a high-NA litho system. The profitable demonstration of high-resolution patterning with the 0.55NA EUV scanner marks a vital milestone in microelectronics manufacturing.

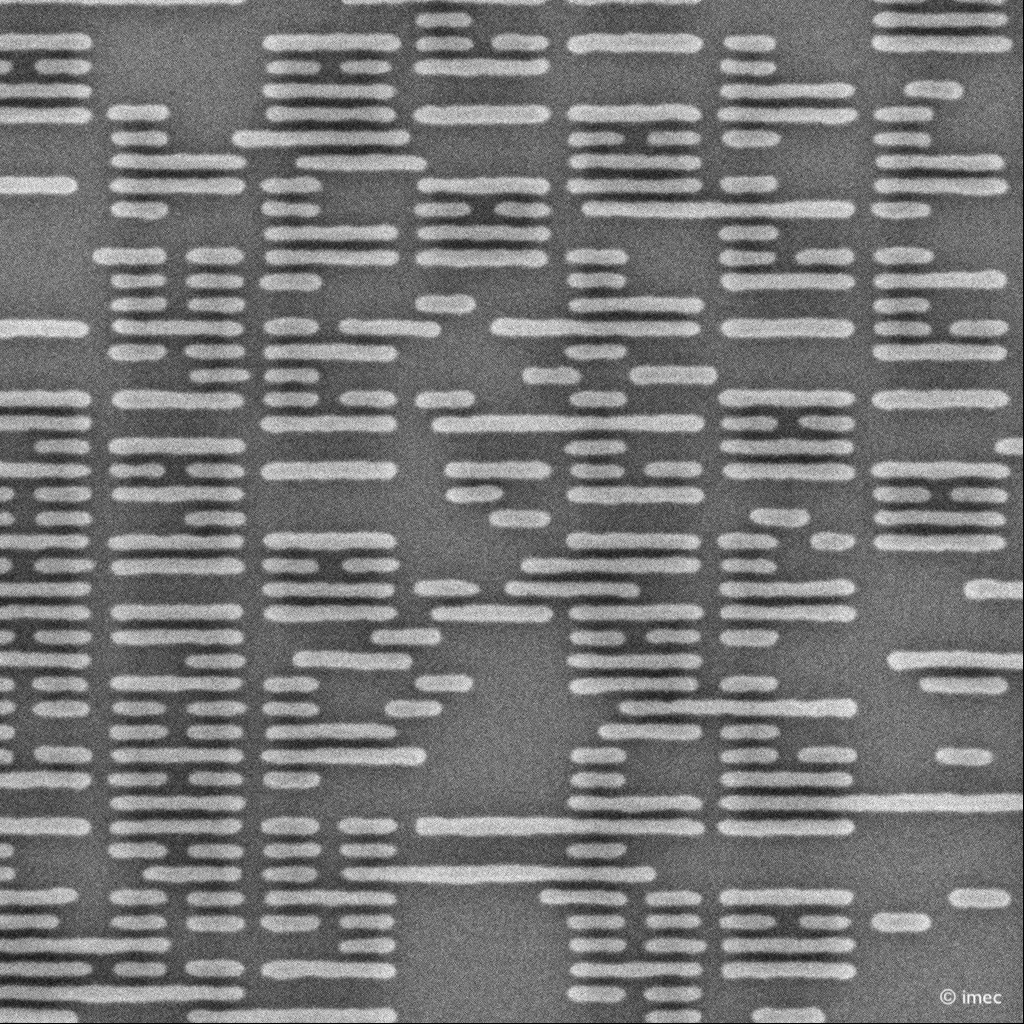

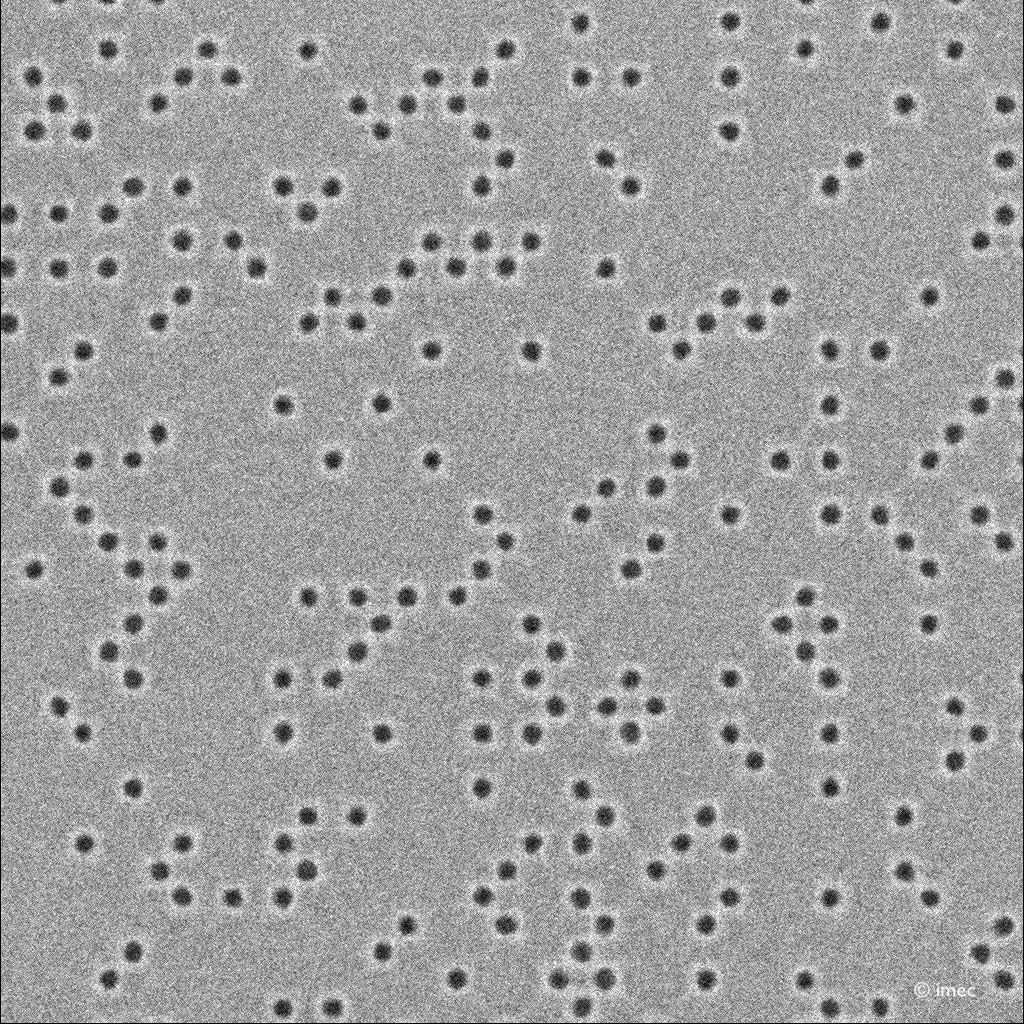

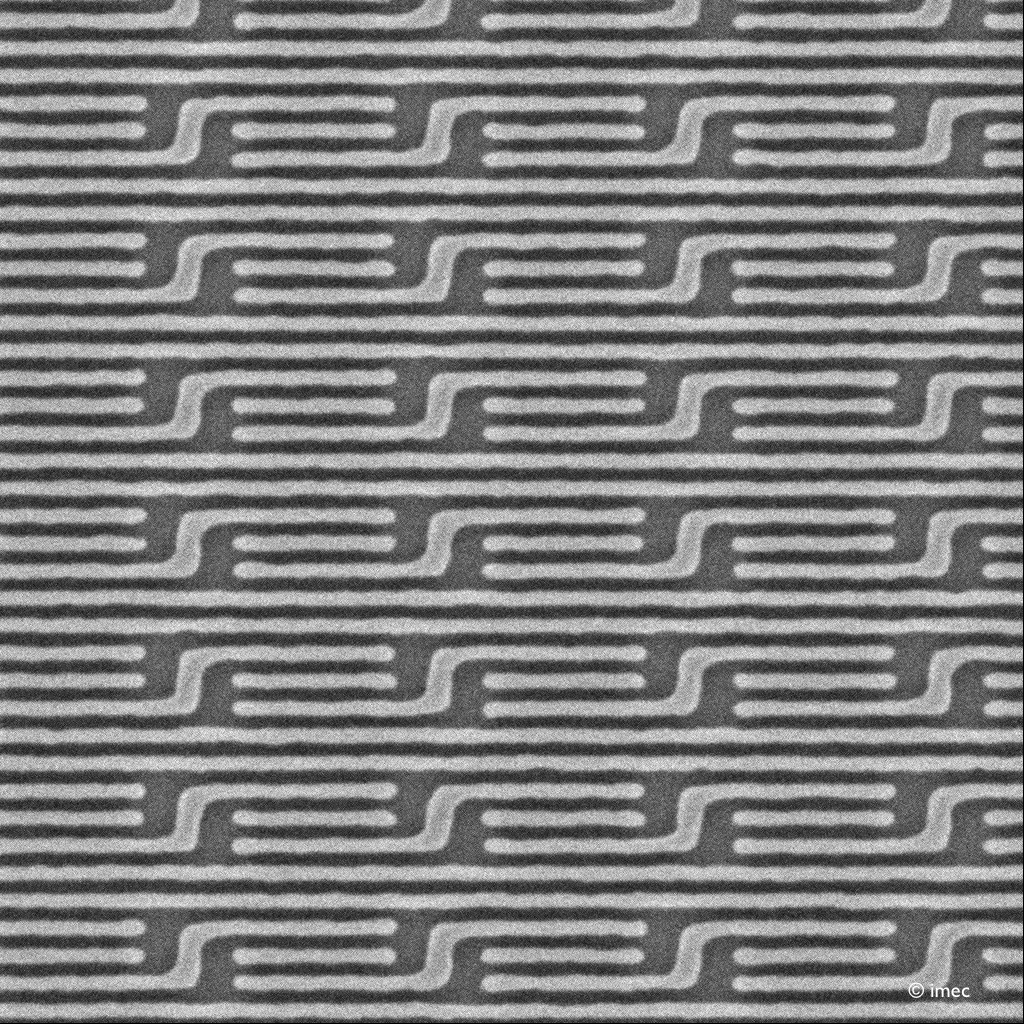

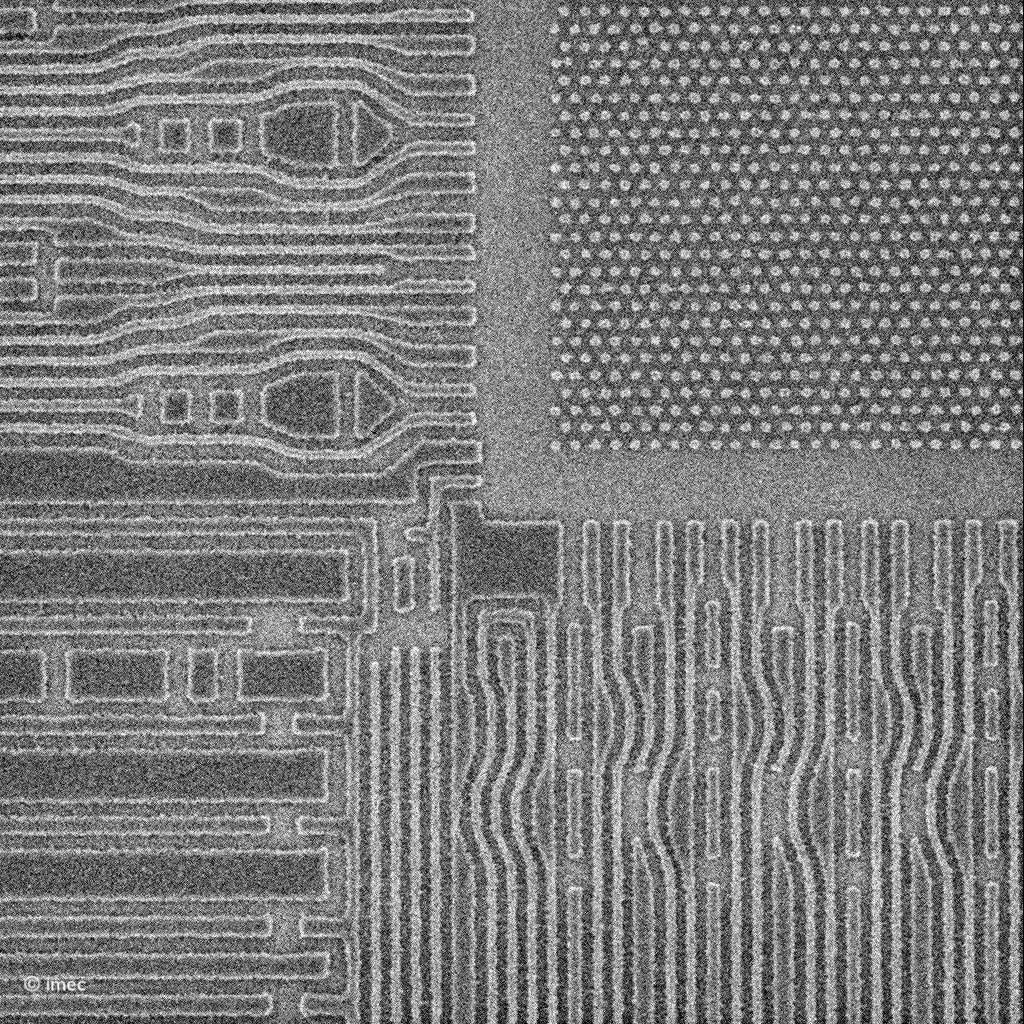

Imec achieved the patterning of random logic constructions with 9.5nm dense metallic traces (in comparison with a 13nm decision within the case of at the moment used Low-NA instruments), which corresponds to a 19nm pitch and a sub 20nm tip-to-tip dimensions, which is sweet sufficient to construct logic on a 1.4nm-class course of expertise utilizing a single Excessive-NA publicity. Moreover, Imec efficiently created random vias with a 30nm center-to-center distance, showcasing good sample constancy and important dimension uniformity. Moreover, 2D options have been patterned at a 22nm pitch, which is sweet sufficient for a 3nm-class fabrication course of.

Contemplating that the pre-production Twinscan EXE Excessive-NA EUV litho system was assembled lower than a yr in the past, the achievements of ASML and Imec on the joint Excessive NA EUV Lithography Lab in Veldhoven, Netherlands, are spectacular, to say the least. This follows printing 10nm dense traces utilizing high-NA EUV in April.

“The outcomes affirm the long-predicted decision functionality of Excessive NA EUV lithography, focusing on sub 20nm pitch metallic layers in a single single publicity,” mentioned Luc Van den Hove, president and CEO of imec. “Excessive NA EUV will subsequently be extremely instrumental to proceed the dimensional scaling of logic and reminiscence applied sciences, one of many key pillars to push the roadmaps deep into the ‘angstrom period’. These early demonstrations have been solely potential due to the setup of the joint ASML-imec lab, which allowed our companions to speed up the introduction of Excessive NA lithography into manufacturing.”

Imec developed sample designs for DRAM layouts that combine the storage node touchdown pad with the bit line periphery at a 32nm pitch in a single publicity. This vital accomplishment underscores Excessive NA expertise’s capacity to interchange a number of masks layers with a single publicity, simplifying manufacturing processes, shrinking cycle occasions, and decreasing prices.

The success of high-NA EUV patterning is attributed to the optimization of supplies and baseline processes by ASML, Imec, and their companions. Preparations concerned creating superior resists, underlayers, and photomasks and transferring Excessive NA EUV baseline processes like optical proximity correction (OPC) and built-in patterning and etch strategies to the 0.55NA EUV scanner.

These outcomes present Excessive NA EUV lithography ecosystem readiness and provides ASML clients an concept of the best way to develop non-public use instances utilizing the Twinscan EXE:5000 lithography system. Imec plans to supply additional insights to assist the maturation of Excessive NA EUV-specific supplies and gear, guaranteeing expertise integration into manufacturing processes.

“We’re thrilled to exhibit the world’s first Excessive NA-enabled logic and reminiscence patterning within the joint ASML-imec lab as an preliminary validation of business purposes,” mentioned Steven Scheer, senior vp of compute applied sciences & programs/compute system scaling at imec.

“The outcomes showcase the distinctive potential for Excessive NA EUV to allow single-print imaging of aggressively-scaled 2D options, enhancing design flexibility in addition to decreasing patterning value and complexity. Trying forward, we anticipate to supply invaluable insights to our patterning ecosystem companions, supporting them in additional maturing Excessive NA EUV particular supplies and gear.”